IBM, IMEC, Samsung ve TSMC’den araştırmacılar, Aralık 2024’te yapılacak olan Uluslararası Elektron Aygıtları Toplantısı’nda (IEDM) dikey istiflenmiş tamamlayıcı alan etkili transistörler (CFET’ler) üzerine son çalışmalarını sunacak. eeNewsEurope’un bildirdiğine göre, CFET’ler gelecekteki teknoloji ölçeklemesini sağlayacak kapılı her yönüyle transistörlerin halefi olarak görülüyor, ancak sektör henüz GAA FET’leri seri üretime geçirebilmiş değil.

n tipi ve p tipi transistörleri üst üste istifleyen CFET konsepti ilk kez 2018’de IMEC araştırma enstitüsü tarafından önerildi. Bugün bile, CFET’in tam anlamıyla uygulanması hala araştırma aşamasında bulunuyor. IMEC’in yol haritasına göre, CFET’ler her şey yolunda giderse A5 düğümüne kadar yaygın üretime ulaşabilir ve bu da 2032 civarında bekleniyor. Intel ve TSMC gibi şirketler ise CFET alanındaki ilerlemelerini son yıllarda göstermeye başladı, bu yüzden IEDM’nin sunacaklarını izlemek önem taşıyor.

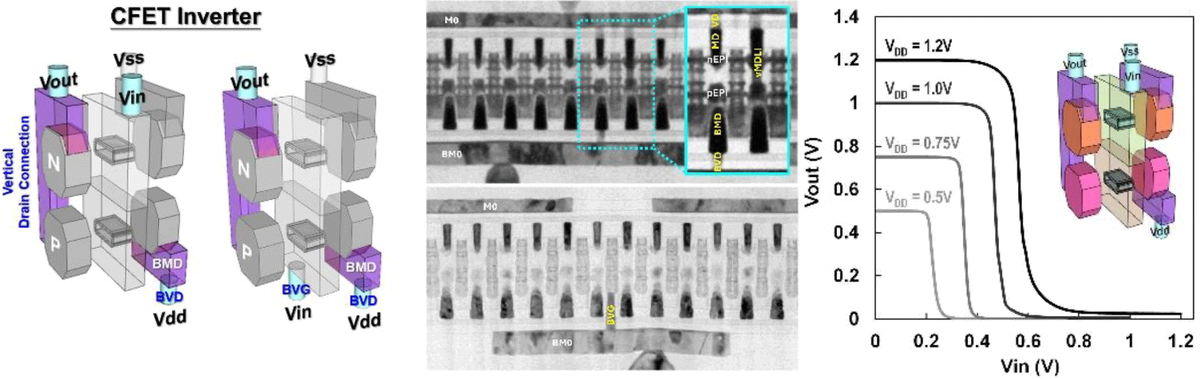

TSMC, 5 nm’lik bir işleme eşdeğer olan 48 nm kapı aralığına sahip monolitik bir CFET invertörü geliştirdiğini açıklayacak. Bu invertör, arka tarafta kontaklı yığınlanmış n tipi ve p tipi nanosheet transistörlere sahiptir ve her iki transistör tipi için 1,2 V’a kadar voltaj transferi sağlarken, 74 ile 76 mV/V arasında bir eşik altı eğimi yakalar. Bu önemli bir dönüm noktası olsa da, TSMC teknolojinin henüz ticari üretime hazır olmadığını belirtiyor.

TSMC’nin tasarımındaki yenilikler arasında dikey drenaj tarafı yerel ara bağlantısı, arka taraf metalize drenaj (BMD) ve arka taraf kapılı geçiş (BVG) bulunuyor. Bu yenilikler, sinyal yönlendirmesini iyileştirirken güç, performans ve alan optimizasyonu (PPA) sağlar.

CFET Teknolojisinin Geleceği

Teknik olarak, bu mimari önümüzdeki yıllarda performans ve enerji verimliliğinde sürekli gelişmeler ve transistör yoğunluğunda artış sağlayabilir. Ancak, TSMC’nin CFET ilerlemelerinin laboratuvar ortamından çıkıp fabrikalarda kullanılabilir hale gelmesi yıllar alabilir.

IBM Research ve Samsung, alt kanalların üst kanallardan daha geniş olduğu, yığın yüksekliğini azaltan ve yüksek en boy oranlarıyla ilgili sorunları hafifleten kademeli bir kanal tasarımı içeren ‘Monolitik Yığılmış FET’ adlı çalışmalarını sunacak. Bu araştırma ayrıca kanallar ve kaynak/drenaj alanları için izolasyon tekniklerini ve çift işlevli metal kullanımını da kapsıyor. Metal ya da kapı aralığı ile ilgili detaylar ise konferansta açıklanacak.

IMEC, CFET’leri hem dikey hem de yatay olarak daha fazla ölçeklendirmek amacıyla geliştirilen ‘Çift Sıralı CFET’ üzerindeki çalışmalarını sunacak. IMEC, bu transistör tasarımının altı ya da yedi nesil ötede bulunan 7a sınıfı (7 angstrom) üretim sürecinde uygulanabilir hale geleceğini öngörüyor. İlginç bir şekilde, ‘Çift Sıralı CFET’ doğrudan arka taraf güç temaslarına sahip değil ve 7 nm düğüme benzer bir şekilde 60 nm kapı aralığına sahip olarak araştırılıyor.

Konferansta sunulacak olan bu makaleler, CFET teknolojisinde önemli ilerlemeler kaydedildiğini gösteriyor. Ancak, bu transistörlerin kitlesel üretime geçmesi yıllar alacak, çünkü üretim karmaşıklığıyla ilgili zorluklar henüz tamamen aşılmadı.

IEDM konferansı 7-11 Aralık 2024 tarihleri arasında San Francisco’da yapılacak ve kayıtlı sunumlara daha sonra çevrimiçi olarak erişilebilecek.